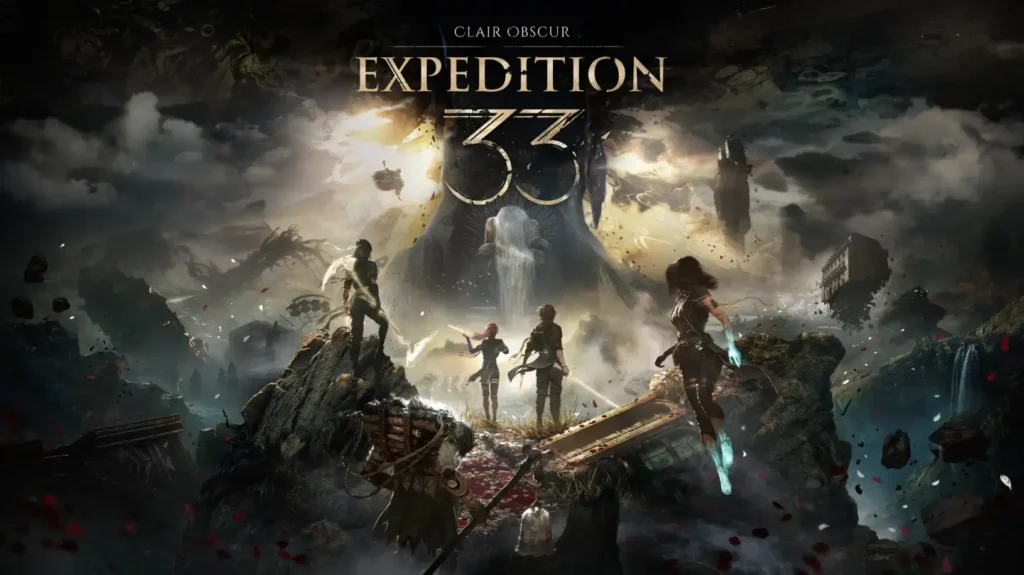

In a world filled with cookie-cutter RPGs, Clair Obscur: Expedition 33 emerges as an exceptional fusion of artistic expression with deeply emotional storytelling. Developed by Sandfall Interactive and released by Kepler Interactive this ambitious game combines turn-based combat mechanics with a painterly atmospheric look and a narrative that maintains constant emotional engagement. This title emerged for PC alongside PlayStation 5 and Xbox Series X|S platforms on April 24, 2025, and it established itself as an RPG with remarkable visual impact and bold thematic exploration.

A World Touched by Mortality

The game unfolds in the gloomy city of Lumière where players encounter a doomed civilization living under constant threat of destruction from a mysterious entity named the Paintress. The Paintress writes a new digit annually on the large stone structure and any individual who reaches that age disappears forever. The core concept serves as both unsettling background and fundamental thematic force that shapes every character’s actions and decisions.

A palpable sense of dread permeates the world where young adventurers embark on a mission to break its fatal cycle. You guide these survivors who represent another unsuccessful attempt to face the Paintress. The story provides no guarantees for a joyful conclusion but instead offers the chance to interrupt a predetermined destiny.

Turn-Based Combat with Real-Time Urgency

Clair Obscur: The gameplay of Expedition 33 transforms classic turn-based mechanics into real-time interactions which require precise player attention. The combat system becomes engaging and modern because players execute attacks through timed inputs that involve parrying and dodging while creating attack synergies. This game manages to maintain player engagement by requiring constant attention and rewarding their focus with rewarding outcomes as opposed to traditional RPGs which suffer from repetitive battles.

The initial battles in the game feel somewhat lackluster. The game’s deeper mechanics remain unused at first because enemies defeat too quickly. Progressing through the game increases difficulty to the point where you must use synergized combos and combat perks called “Pictos” as essential tools. Pictos serve as stat modifiers that progressively become more potent over time and provide a customized gameplay experience which motivates players to explore different builds and strategic methods.

A Cast That Feels Undeniably Human

Clair Obscur achieves remarkable success through its exceptional writing and voice acting. Charlie Cox (Daredevil) and Jennifer English (Baldur’s Gate 3) lead a stellar cast that infuses the characters with heart-wrenching realism. Their motivations, fears, and internal struggles are etched into every conversation and decision, reinforcing the game’s overarching theme: how do we confront the inescapable?

Your party members stand out as fully developed characters who both possess depth and play crucial roles in the story. The characters’ relationships develop organically through a combination of situational factors and their personal decisions. This story provides entertainment that continues to resonate beyond its conclusion. The consequences of their actions will stay with you long after you finish playing the game.

Art and Atmosphere Worthy of a Museum

The visual presentation in Clair Obscur: Expedition 33 is nothing short of breathtaking. The game environments blend Belle Époque-era French aesthetics with a surrealist touch to create spaces that feel simultaneously mystical and deteriorating and embody the game’s dual themes. Every location in this world showcases a blend of beauty and sorrow as it silently narrates tales of loss and hope.

The smallest UI elements along with battle animations show the same high level of attention to detail. The game becomes a responsive masterpiece because each frame displays intentional artistry. The artwork serves a purpose beyond aesthetics by strengthening player immersion and improving each gameplay moment.

More Than Just an Enemy: The Paintress and the Internal Fight

The Paintress functions as the main antagonist but symbolizes deeper themes rather than being a traditional monster. The nature of what she embodies—inevitability and death alongside grief—defines the true struggle for the characters. The emotional resonance of the game stems from its conceptual layering. The game demands players face the loss-induced helplessness and their instinctive resistance toward it despite its futility when confronting boss battles.

As the story progresses external and internal conflicts become increasingly indistinguishable. The most dangerous adversaries exist both externally and internally as they reside within the party members themselves. The combination of deep storytelling and personal risks transforms each expedition into a deeply moving experience.

Final Verdict

Clair Obscur: Expedition 33 provides players with an immersive experience beyond typical gameplay. This game tests your combat reflexes while simultaneously engaging your emotions through dialogue. The game explores complex themes of mortality and loss while leaving the answers to these questions intentionally ambiguous. The initial pacing of the game may seem erratic but those who decide to explore its depths will discover an exceptional RPG experience for the decade.

For players who appreciate titles like Persona, NieR: The game Clair Obscur: Expedition 33 becomes essential for those seeking emotional depth from their games especially if they love titles like NieR: Automata or Final Fantasy.

Rating: ★★★★½ (4.5/5)